Markt für Chip-zu-Chip-IP – Berichtsumfang und Überblick:

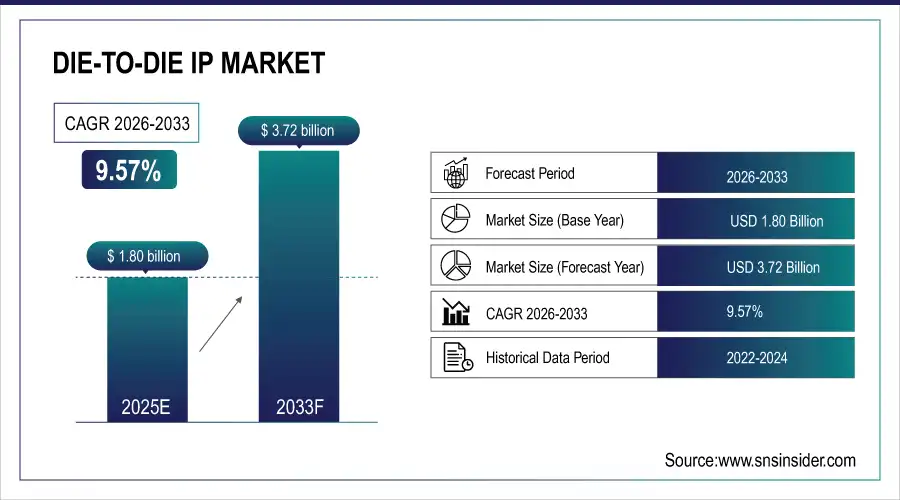

Der Markt für Die-to-Die IP hatte im Jahr 2025 einen Wert von 1,80 Milliarden US-Dollar und wird bis 2033 voraussichtlich auf 3,72 Milliarden US-Dollar anwachsen, was einem durchschnittlichen jährlichen Wachstum von 9,57 % im Zeitraum 2026-2033 entspricht.

Der Markt für Die-to-Die-IP wächst aufgrund der rasanten Verbreitung chipletbasierter Architekturen, die im Vergleich zu monolithischen Chips höhere Leistung, geringeren Stromverbrauch und reduzierte Entwicklungskosten ermöglichen. Die steigende Nachfrage nach KI-Beschleunigern, Hochleistungsrechnern und Rechenzentrumsprozessoren treibt den Bedarf an Verbindungen mit hoher Bandbreite und geringer Latenz voran. Fortschritte bei 2,5D- und 3D-Packaging, die zunehmende Verbreitung des UCIe-Standards und die wachsende Komplexität von Halbleitern unterstützen die Marktexpansion in den Bereichen Automobil, Konsumgüter und Industrieanwendungen zusätzlich.

Marktgröße und Wachstumsprognose:

-

Marktgröße im Jahr 2025 (Schätzung): 1,80 Milliarden US-Dollar

-

Marktgröße bis 2033: 3,72 Milliarden US-Dollar

-

Jährliche Wachstumsrate von 9,57 % von 2026 bis 2033

-

Basisjahr 2025E

-

Prognosezeitraum 2026-2033

-

Historische Daten 2021-2024

Um mehr Informationen zum Die-to-Die IP-Markt zu erhalten, fordern Sie einen kostenlosen Musterbericht an.

Wichtigste Trends im Die-to-Die-IP-Markt

-

Rasante Verbreitung von Chiplet-basierten Architekturen, die traditionelle monolithische SoC-Designs ersetzen und dadurch eine höhere Leistung und Effizienz erzielen.

-

Wachsende Nachfrage aus den Bereichen HPC, KI, maschinelles Lernen und Rechenzentrumsprozessoren, die hochbandbreitige Die-zu-Die-Verbindungen mit geringer Latenz erfordern.

-

Fortschritte bei der 2,5D- und 3D-IC-Gehäusetechnik und zunehmende Nutzung offener Standards wie UCIe für Interoperabilität.

-

Erweiterung des Chiplet-Ökosystems in den Bereichen Automobilindustrie, ADAS und autonomes Fahren mit sicherheitskritischen Leistungsanforderungen.

-

Zunehmende Investitionen von Hyperscalern und System-OEMs in die Halbleiterfertigung im asiatisch-pazifischen Raum, in fortschrittliche Gehäusetechnologien und in die kundenspezifische Siliziumentwicklung.

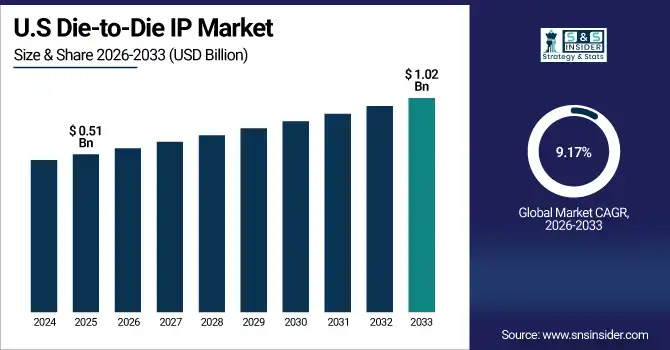

Der US-amerikanische Markt für Die-to-Die-IP wurde 2025 auf 0,51 Milliarden US-Dollar geschätzt und soll bis 2033 auf 1,02 Milliarden US-Dollar anwachsen, was einer durchschnittlichen jährlichen Wachstumsrate (CAGR) von 9,17 % im Zeitraum 2026–2033 entspricht. Das Wachstum des US-amerikanischen Die-to-Die-IP-Marktes ist auf starke Investitionen in KI und Hochleistungsrechnen, die rasche Einführung von Chiplet-Architekturen durch führende Halbleiterunternehmen, die führende Rolle bei fortschrittlichen Packaging-Technologien sowie die steigende Nachfrage von Hyperscalern nach energieeffizienten Verbindungslösungen mit hoher Bandbreite zurückzuführen.

Wachstumstreiber des Die-to-Die-IP-Marktes:

-

Der rasante Wandel hin zu Chiplet-Architekturen treibt das Wachstum des globalen Die-to-Die-IP-Marktes in den Bereichen HPC, KI und Advanced Packaging voran.

Der globale Markt für Die-to-Die-IP wird primär durch den rasanten Übergang von monolithischen System-on-Chip-Designs zu Chiplet-basierten Architekturen angetrieben. Diese ermöglichen höhere Leistung, verbesserte Ausbeute und geringere Entwicklungskosten. Die steigende Nachfrage nach Hochleistungsrechnern, künstlicher Intelligenz, maschinellem Lernen und Rechenzentrumsprozessoren erfordert Verbindungslösungen mit extrem hoher Bandbreite, geringer Latenz und hoher Energieeffizienz zwischen mehreren Dies. Fortschritte bei fortschrittlichen Packaging-Technologien wie der 2,5D- und 3D-IC-Integration sowie die zunehmende Verbreitung offener Standards wie UCIe beschleunigen die Interoperabilität und die Reife des Ökosystems. Darüber hinaus verstärken die steigende Komplexität des Halbleiterdesigns bei fortschrittlichen Fertigungsknoten und die Notwendigkeit, die Leistungs- und Wärmeeffizienz zu optimieren, die Verwendung von Die-to-Die-Interconnect-IP in Anwendungen der Automobilindustrie, der Netzwerktechnik und der Unterhaltungselektronik.

Chiplet-basierte Designs generieren mittlerweile einen Jahresumsatz von rund 40 Milliarden US-Dollar, was zeigt, wie weit verbreitet die modulare Multi-Die-Integration in der Hochleistungselektronik geworden ist.

Beschränkungen des IP-Marktes im Bereich Die-to-Die:

-

Markt für Chip-zu-Chip-IP durch Standardisierungsherausforderungen, komplexe Designs und Einschränkungen im Wärmemanagement eingeschränkt

Der Markt für Die-to-Die-IP stößt aufgrund der begrenzten Standardisierung nach der frühen Einführung von UCIe auf Einschränkungen, was zu Interoperabilitätsproblemen zwischen verschiedenen Anbietern und Ökosystemen führt. Designkomplexität, Probleme mit der Signalintegrität bei hohen Datenraten und Einschränkungen beim Wärmemanagement in modernen Gehäusen behindern eine schnellere Verbreitung. Darüber hinaus verlangsamen lange Qualifizierungszyklen in Automobil- und Industrieanwendungen sowie Herausforderungen bei der IP-Integration und -Validierung auf heterogenen Chips den großflächigen Einsatz.

Marktchancen für die Die-to-Die-IP-Branche:

-

Die Erweiterung des Chiplet-Ökosystems eröffnet globale IP-Möglichkeiten im Bereich der Automobil-KI und in Schwellenländern.

Mit der Ausweitung des Chiplet-Ökosystems auf neue Anwendungsbereiche jenseits von HPC und Rechenzentren eröffnen sich bedeutende Chancen. Automobilelektronik, einschließlich ADAS und Plattformen für autonomes Fahren, birgt aufgrund steigender Rechenanforderungen und sicherheitskritischer Leistungsanforderungen ein starkes Wachstumspotenzial. Schwellenländer im asiatisch-pazifischen Raum schaffen durch hohe Investitionen in die Halbleiterfertigung, fortschrittliche Gehäusetechnologien und nationale Chipdesign-Initiativen neue Möglichkeiten. Darüber hinaus eröffnet die zunehmende Beteiligung von Hyperscalern und System-OEMs an der kundenspezifischen Siliziumentwicklung neue Nachfrage nach skalierbaren, standardisierten Die-to-Die-IP-Lösungen. Kontinuierliche Innovationen in den Bereichen 3D-Stacking, heterogene Integration und offene Schnittstellenstandards werden weltweit weitere langfristige Wachstumschancen erschließen.

Die elektrische Limousine P7+ von Xpeng nutzt zwei Nvidia Orin X-Prozessoren, um über 500 TOPS Rechenleistung aus mehreren Sensoreingängen zu liefern. Dies zeigt den realen Einsatz von Hochleistungsrechnern in Fahrzeugen, die von modularen Chiplets profitieren könnten.

Marktsegmentanalyse für Die-to-Die IP

-

Nach Schnittstellenstandard dominierte UCIe (Universal Chiplet Interconnect Express) mit 53,43 % im Jahr 2025E und wird voraussichtlich von 2026 bis 2033 mit der schnellsten durchschnittlichen jährlichen Wachstumsrate (CAGR) von 9,92 % wachsen.

-

Nach Verpackungstechnologie dominierte die 2,5D-IC-Verpackung mit 39,97 % im Jahr 2025E, während für die 3D-IC-Verpackung von 2026 bis 2033 das schnellste Wachstum mit einer durchschnittlichen jährlichen Wachstumsrate (CAGR) von 10,10 % erwartet wird.

-

Nach Anwendungsbereich dominierten High-Performance Computing (HPC) und KI-Beschleuniger mit 41,86 % im Jahr 2025E, und es wird erwartet, dass sie von 2026 bis 2033 mit der schnellsten durchschnittlichen jährlichen Wachstumsrate (CAGR) von 9,83 % wachsen werden.

-

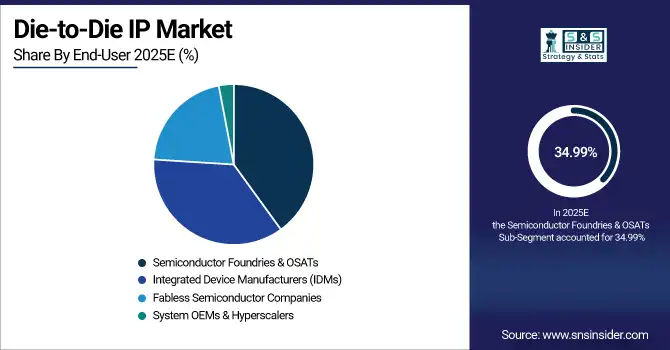

Nach Endnutzer dominierten Halbleitergießereien und OSATs mit 34,99 % im Jahr 2025E, Fabless-Halbleiterunternehmen werden voraussichtlich von 2026 bis 2033 mit einer durchschnittlichen jährlichen Wachstumsrate (CAGR) von 10,12 % am schnellsten wachsen.

Nach Endnutzer betrachtet führen Halbleiterhersteller den Markt für Die-to-Die-IP bis 2025 an, während Fabless-Unternehmen das zukünftige Wachstum vorantreiben.

Halbleiter-Foundries und OSATs dominieren den Die-to-Die-IP-Markt im Jahr 2025. Treiber dieses Wachstums sind ihre Rolle in den Bereichen Advanced Packaging, Multi-Die-Integration und die Bereitstellung skalierbarer Lösungen für diverse Kunden in den Bereichen HPC, KI und Automobilindustrie. Fabless-Halbleiterunternehmen werden voraussichtlich von 2026 bis 2033 das schnellste Wachstum verzeichnen, da sie zunehmend standardisierte Chiplet-Architekturen und Die-to-Die-IP einsetzen, um die Markteinführungszeit zu verkürzen, die Leistung zu steigern und die Designkomplexität zu reduzieren. Unterstützt wird diese Entwicklung durch die wachsende Zusammenarbeit mit Foundries, System-OEMs und Hyperscalern weltweit.

Nach Schnittstellenstandard dominiert der UCIe-Standard den Markt bis 2025 und treibt das rasante zukünftige Wachstum der Chiplet-Integration voran.

Der UCIe-Standard (Universal Chiplet Interconnect Express) wird aufgrund seiner offenen, interoperablen Architektur, die eine nahtlose Kommunikation zwischen Chiplets verschiedener Hersteller ermöglicht, im Jahr 2025 dominieren. Seine Verbreitung in Hochleistungsrechnern, KI-Beschleunigern und Rechenzentrumsprozessoren sorgt für breite Branchenunterstützung. UCIe wird voraussichtlich von 2026 bis 2033 am schnellsten wachsen, angetrieben durch die steigende Nachfrage nach modularen, bandbreitenstarken und energieeffizienten Multi-Die-Systemen, wachsende Chiplet-Ökosysteme und kontinuierliche Innovationen in der heterogenen Integration und fortschrittlichen Packaging-Technologien.

Nach Verpackungstechnologie führt 2,5D-IC-Gehäuse den Markt bis 2025 an, während 3D-IC-Gehäuse das zukünftige Wachstum von Chip zu Chip beschleunigen.

Die 2,5D-IC-Gehäusetechnologie wird aufgrund ihrer ausgereiften Technologie, Kosteneffizienz und der Möglichkeit, mehrere Chips auf einem Interposer zu integrieren, im Jahr 2025 dominieren und bietet hohe Leistung und zuverlässige Konnektivität für HPC-, KI- und Rechenzentrumsanwendungen. Die 3D-IC-Gehäusetechnologie wird voraussichtlich von 2026 bis 2033 am schnellsten wachsen, angetrieben durch die steigende Nachfrage nach höherer Verbindungsdichte, verbesserter Energieeffizienz und fortschrittlicher heterogener Integration in KI-Beschleunigern, Automobilelektronik und Computersystemen der nächsten Generation. Kontinuierliche Innovationen im Bereich des vertikalen Stapelns und des Wärmemanagements unterstützen dieses Wachstum.

Anwendungsbezogen treiben HPC- und KI-Beschleuniger den Die-to-Die-IP-Markt bis 2025 mit rasantem zukünftigem Wachstum voran.

Hochleistungsrechner (HPC) und KI-Beschleuniger werden den Markt für Chip-zu-Chip-IP im Jahr 2025 voraussichtlich dominieren. Grund dafür ist der rasante Anstieg von KI-Workloads, Deep Learning und komplexen Simulationen, die extrem hohe Bandbreiten und latenzarme Verbindungen erfordern. Dieses Anwendungssegment wird voraussichtlich auch von 2026 bis 2033 am schnellsten wachsen, angetrieben durch die zunehmende Verbreitung von KI, Exascale-Computing-Initiativen und die steigende Nachfrage von Rechenzentren und Cloud-Anbietern. Kontinuierliche Innovationen bei Chiplet-Architekturen und der Chip-zu-Chip-Integration beschleunigen den Einsatz in HPC- und KI-Systemen zusätzlich.

Einblicke in den nordamerikanischen Markt für Die-to-Die-IP

Nordamerika, das 2025 voraussichtlich 36,36 % des Marktes für Die-to-Die-IP halten wird, ist aufgrund seines starken Halbleiter-Ökosystems, der Präsenz führender Chiplet- und IP-Anbieter sowie der frühen Einführung fortschrittlicher Packaging- und UCIe-Standards die dominierende Region. Die Region profitiert von signifikanten Investitionen in Forschung und Entwicklung, einer robusten Rechenzentrumsinfrastruktur und wachsenden Anwendungen im Bereich KI und HPC. Die enge Zusammenarbeit zwischen Fabless-Unternehmen, Foundries und Hyperscalern stärkt Nordamerikas führende Position im Bereich der Die-to-Die-Verbindungstechnologie und von Hochleistungsrechnerlösungen zusätzlich.

Erhalten Sie einen maßgeschneiderten Bericht gemäß Ihren Geschäftsanforderungen – Jetzt anfragen!

Einblicke in den US-amerikanischen Markt für die Chiptechnologie (Die-to-Die IP)

Die Vereinigten Staaten dominieren den nordamerikanischen Die-to-Die-IP-Markt aufgrund der Konzentration führender Halbleiterunternehmen, fortschrittlicher Forschungs- und Entwicklungseinrichtungen, der frühen Einführung von Chiplet-Architekturen und der starken Präsenz von Hyperscalern und Hochleistungsrechnerinfrastruktur.

Einblicken in den europäischen Markt für Die-to-Die-IP

Europa, das 2025 voraussichtlich 16,97 % des Marktes für Die-to-Die-IP ausmachen wird, hält einen moderaten Anteil, der durch Halbleiterinnovationen in Deutschland, Frankreich und den Niederlanden getragen wird. Die Region konzentriert sich auf Automobilelektronik, industrielle Automatisierung und Verteidigungsanwendungen, unterstützt durch fortschrittliche Forschung im Bereich Packaging und gemeinsame Chiplet-Initiativen. Ein starker Fokus auf Standardisierung, energieeffiziente Designs und staatlich geförderte Halbleiterprogramme stärkt Europas Rolle im globalen Ökosystem für Die-to-Die-Verbindungen.

Einblicken in den deutschen Markt für Die-to-Die-IP

Deutschland dominiert den europäischen Markt für Die-to-Die-IP aufgrund seiner starken Halbleiterindustrie für die Automobilindustrie, seiner fortschrittlichen Forschung im Bereich Chiplet- und Packaging-Technologien sowie seiner Führungsrolle in der industriellen Automatisierung und ist damit der Hauptakteur im europäischen Ökosystem für Die-to-Die-Verbindungen.

Einblicke in den asiatisch-pazifischen Markt für Die-to-Die-IP

Im Markt für Die-to-Die-IP wird im asiatisch-pazifischen Raum voraussichtlich von 2026 bis 2033 mit einer durchschnittlichen jährlichen Wachstumsrate (CAGR) von 10,25 % das schnellste Wachstum verzeichnen. Treiber dieser Entwicklung ist der rasante Ausbau der Halbleiterfertigung in China, Taiwan, Südkorea und Japan. Investitionen in fortschrittliche Gehäusetechnologien, Chiplet-Design und nationale Halbleiterinitiativen fördern die Akzeptanz dieser Technologien. Die steigende Nachfrage nach Anwendungen in den Bereichen KI, HPC, Unterhaltungselektronik und Automobilindustrie, kombiniert mit staatlicher Unterstützung und der zunehmenden Präsenz von Fabless-Unternehmen und Foundries, positioniert den asiatisch-pazifischen Raum als den weltweit am schnellsten wachsenden regionalen Markt.

Einblicke in den chinesischen Markt für Die-to-Die-IP

China dominiert den asiatisch-pazifischen Markt für Die-to-Die-IP aufgrund seiner massiven Investitionen in die Halbleiterfertigung, fortschrittliche Verpackungsanlagen, Chiplet-Forschung und -Entwicklung, staatlich unterstützte Initiativen und die wachsende Nachfrage aus den Bereichen KI, HPC, Automobilindustrie und Unterhaltungselektronik.

Markteinblicke für Die-to-Die-IP in Lateinamerika (LATAM) und im Nahen Osten & Afrika (MEA).

Lateinamerika (LATAM) und der Nahe Osten & Afrika (MEA) halten zwar kleinere Anteile am Die-to-Die-IP-Markt, weisen aber wachsendes Potenzial auf. LATAM profitiert von der zunehmenden Verbreitung von Automobilelektronik, industrieller Automatisierung und der entstehenden Rechenzentrumsinfrastruktur, während sich MEA auf Anwendungen in den Bereichen Verteidigung, Energie und Telekommunikation konzentriert. Investitionen in die Halbleiterausbildung, lokale Fertigungsinitiativen und Partnerschaften mit globalen Technologieanbietern stärken die Kompetenzen schrittweise. Obwohl die Einführung langsamer verläuft als in Nordamerika, Europa und im asiatisch-pazifischen Raum, bieten diese Regionen Chancen für Nischenanwendungen und strategische Expansion.

Wettbewerbsumfeld für den Die-to-Die-IP-Markt:

Synopsys, Inc. ist ein weltweit führender Anbieter von EDA-Tools (Electronic Design Automation) und Halbleiter-IP, einschließlich Die-to-Die-Verbindungslösungen. Das Unternehmen bietet leistungsstarke, UCIe-konforme IP, fortschrittliche PHYs, Controller und Verifikationsplattformen für Multi-Die-Chiplet-Architekturen in HPC, KI, Rechenzentren, der Automobilindustrie und der Unterhaltungselektronik. Synopsys treibt Innovationen in der heterogenen Integration und im Advanced Packaging voran und unterstützt Halbleiterunternehmen dabei, Designzyklen zu beschleunigen, die Leistung zu optimieren und zuverlässige Verbindungen mit hoher Bandbreite zu realisieren.

-

Im September 2024 kündigte Synopsys eine UCIe-IP-Suite mit 40 Gbit/s pro Pin an. Diese umfasst Controller-, PHY- und Verifizierungs-IP und ermöglicht so extrem hohe Bandbreiten für die Chip-zu-Chip-Konnektivität in Multi-Die-KI-Rechenzentrumschips. Die Lösung bietet verbesserte Signalintegritätsüberwachung und umfassende Unterstützung für Verbindungen.

Cadence Design Systems, Inc. ist ein führender Anbieter von EDA-Tools (Electronic Design Automation) und Halbleiter-IP mit Spezialisierung auf Die-to-Die-Verbindungen und Chiplet-Lösungen. Das Unternehmen bietet UCIe-konforme IP, Hochgeschwindigkeits-PHYs, Controller und Verifikationsplattformen für Multi-Die-Architekturen in HPC-, KI-, Rechenzentrums-, Automobil- und Konnektivitätsanwendungen. Cadence ermöglicht schnellere Markteinführungen, leistungsstarke Integration und skalierbare heterogene Designs und fördert so die weltweite Einführung fortschrittlicher Packaging-Technologien und Halbleitertechnologien der nächsten Generation.

-

Im April 2025 kündigte Cadence eine bedeutende Erweiterung seines Design-IP-Portfolios an, darunter UCIe 1.1 48G Die-to-Die-Interconnect-IP und fortschrittliche Interface-IP, die für Intels 18A- und 18A-P-Technologien optimiert sind, um KI-, HPC- und Mobilitätsdesigns zu beschleunigen.

Die-to-Die IP-Unternehmen sind:

-

Synopsys

-

Cadence Design Systems

-

Arm Holdings

-

Marvell Technology

-

Alphawave Semi

-

Rambus

-

Arterie

-

Blue Cheetah Analog Design

-

VeriSilicon

-

OpenFive

-

OPENEDGES-Technologie

-

Siemens EDA

-

Texas Instruments

-

NXP Halbleiter

-

Infineon Technologies

-

STMicroelectronics

-

Renesas Electronics

-

Mikrochip-Technologie

-

Analog Devices

-

ON Semiconductor

| Berichtsattribute | Details |

|---|---|

| Marktgröße im Jahr 2025E | 1,80 Milliarden US-Dollar |

| Marktgröße bis 2033 | 3,72 Milliarden US-Dollar |

| CAGR | Jährliche Wachstumsrate von 9,57 % von 2026 bis 2033 |

| Basisjahr | 2025E |

| Prognosezeitraum | 2026–2033 |

| Historische Daten | 2021-2024 |

| Berichtsumfang und -abdeckung | Marktgröße, Segmentanalyse, Wettbewerbsumfeld, regionale Analyse, DROC- und SWOT-Analyse, Prognoseausblick |

| Schlüsselsegmente | • Nach Schnittstellenstandard (UCIe (Universal Chiplet Interconnect Express), BoW (Bunch of Wires), proprietäre/kundenspezifische Schnittstellen und neue offene Standards) • Nach Gehäusetechnologie (2,5D-IC-Gehäuse, 3D-IC-Gehäuse, Fan-Out-Wafer-Level-Packaging (FOWLP) und System-in-Package (SiP)) • Nach Anwendung (Hochleistungsrechnen (HPC) & KI-Beschleuniger, Rechenzentren & Cloud-Infrastruktur, Unterhaltungselektronik und Automobilelektronik) • Nach Endnutzer (Halbleiter-Foundries & OSATs, integrierte Gerätehersteller (IDMs), Fabless-Halbleiterunternehmen und System-OEMs & Hyperscaler) |

| Regionale Analyse/Abdeckung | Nordamerika (USA, Kanada), Europa (Deutschland, Großbritannien, Frankreich, Italien, Spanien, Russland, Polen, übriges Europa), Asien-Pazifik (China, Indien, Japan, Südkorea, Australien, ASEAN-Staaten, übriges Asien-Pazifik), Naher Osten und Afrika (VAE, Saudi-Arabien, Katar, Südafrika, übriger Naher Osten und Afrika), Lateinamerika (Brasilien, Argentinien, Mexiko, Kolumbien, übriges Lateinamerika). |

| Firmenprofile | Synopsys, Cadence Design Systems, Arm Holdings, Marvell Technology, Alphawave Semi, Rambus, Arteris, Blue Cheetah Analog Design, VeriSilicon, OpenFive, OPENEDGES Technology, Siemens EDA, Texas Instruments, NXP Semiconductors, Infineon Technologies, STMicroelectronics, Renesas Electronics, Microchip Technology, Analog Devices, ON Semiconductor. |

Häufig gestellte Fragen

Antwort: Der Markt für Die-to-Die-IP wird voraussichtlich von 2026 bis 2033 mit einer durchschnittlichen jährlichen Wachstumsrate (CAGR) von 9,57 % wachsen.

Antwort: Der Markt für Die-to-Die-IP hatte im Jahr 2025 ein Volumen von 1,80 Milliarden US-Dollar und wird voraussichtlich bis 2033 auf 3,72 Milliarden US-Dollar anwachsen.

Antwort: Der Markt für Die-to-Die-IP wird durch die zunehmende Verbreitung von Chiplet-Architekturen, die wachsende Nachfrage nach Hochleistungsrechnern und KI sowie durch Fortschritte bei 2,5D/3D-Packaging mit standardisierten Verbindungen wie UCIe angetrieben.

Antwort: UCIe (Universal Chiplet Interconnect Express) dominierte den Die-to-Die IP-Markt.

Antwort: Nordamerika dominierte den Die-to-Die IP-Markt im Jahr 2025E.