ダイツーダイIP市場 - レポートの範囲と概要:

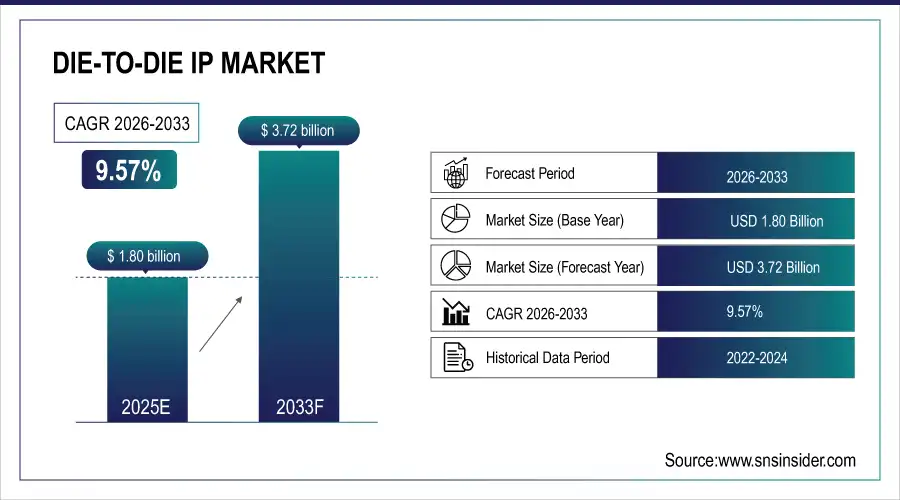

Die-to-Die IP 市場規模は 2025 年に 18 億米ドルと評価され、2026 年から 2033 年にかけて 9.57% の CAGR で成長し、2033 年までに 37.2 億米ドルに達すると予測されています。

Die-to-Die IP市場は、モノリシックチップと比較して高性能、低消費電力、そして設計コストの削減を可能にするチップレットベースのアーキテクチャの急速な導入により成長を続けています。AIアクセラレータ、高性能コンピューティング、データセンタープロセッサの需要増加により、高帯域幅・低レイテンシのインターコネクトの必要性が高まっています。2.5Dおよび3Dパッケージングの進歩、UCIe規格の採用拡大、そして半導体の複雑化は、自動車、民生、産業用途における市場拡大をさらに後押ししています。

市場規模と成長予測:

-

2025年の市場規模は18億ドル

-

2033年までの市場規模 37億2000万米ドル

-

2026年から2033年までのCAGRは9.57%

-

基準年2025E

-

予測期間 2026~2033年

-

2021~2024年の履歴データ

Die-to-Die IP市場に関する詳細情報を入手するには、無料のサンプルレポートをリクエストしてください。

ダイツーダイIP市場の主要動向

-

より高いパフォーマンスと効率性を実現するために、従来のモノリシック SoC 設計に代わるチップレット ベースのアーキテクチャを急速に採用しています。

-

高帯域幅、低レイテンシのダイ間相互接続を必要とする HPC、AI、機械学習、データ センター プロセッサからの需要が高まっています。

-

2.5D および 3D IC パッケージングの進歩と、相互運用性のための UCIe などのオープン スタンダードの使用の増加。

-

安全性が極めて重要なパフォーマンスが求められる自動車、ADAS、自律運転アプリケーションへのチップレット エコシステムの拡張。

-

ハイパースケーラーおよびシステム OEM によるアジア太平洋地域の半導体製造、高度なパッケージング、カスタム シリコン開発への投資が増加しています。

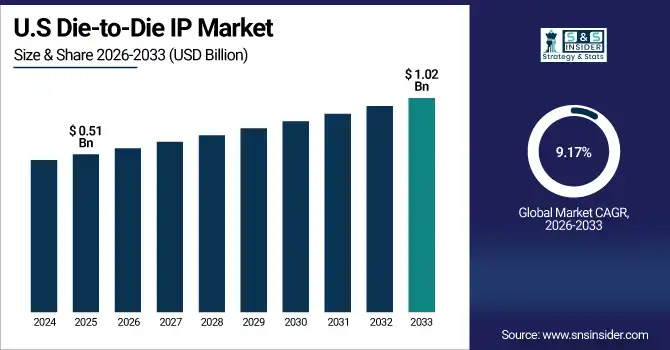

米国のDie-to-Die IP市場規模は、2025年推計で5億1,000万米ドルと評価され、2033年には10億2,000万米ドルに達すると予測されています。2026年から2033年にかけては年平均成長率(CAGR)9.17%で成長が見込まれます。米国のDie-to-Die IP市場は、AIと高性能コンピューティングへの旺盛な投資、大手半導体企業によるチップレットアーキテクチャの急速な導入、先進的なパッケージングにおけるリーダーシップ、そしてハイパースケーラーによる高帯域幅かつエネルギー効率の高い相互接続ソリューションへの需要増加により、成長を続けています。

Die-to-Die IP 市場の成長要因:

-

チップレットアーキテクチャへの急速な移行が、HPC AIおよび先進パッケージングにおける世界のDie-to-Die IP市場の成長を促進

世界のDie-to-Die IP市場は、モノリシックなシステムオンチップ設計から、高性能、歩留まり向上、開発コスト削減を実現するチップレットベースのアーキテクチャへの急速な移行によって牽引されています。高性能コンピューティング、人工知能(AI)、機械学習、データセンター向けプロセッサの需要が高まるにつれ、複数のダイ間を接続する超高帯域幅、低レイテンシ、そしてエネルギー効率に優れた相互接続ソリューションが求められています。2.5Dおよび3D IC統合といった高度なパッケージング技術の進歩と、UCIeなどのオープンスタンダードの採用拡大は、相互運用性とエコシステムの成熟を加速させています。さらに、先端ノードにおける半導体設計の複雑さの増大と、電力効率と熱効率の最適化の必要性から、自動車、ネットワーキング、民生用電子機器といったアプリケーションにおいて、Die-to-Die相互接続IPの採用が加速しています。

チップレットベースの設計は現在、年間約 400 億米ドルの収益を生み出しており、高性能電子機器においてモジュラーマルチダイ統合がいかに普及しているかを示しています。

Die-to-Die IP 市場の制約:

-

ダイツーダイIP市場は標準化の課題、複雑な設計、熱管理の制限によって制約を受けている

Die-to-Die IP市場は、UCIeの早期導入以降、標準化が限定的であることから制約を受けており、ベンダーやエコシステム間で相互運用性の課題が生じています。設計の複雑さ、高データレートにおけるシグナルインテグリティの問題、そして先進的なパッケージングにおける熱管理の制約が、迅速な導入を阻害しています。さらに、車載・産業用アプリケーションにおける長期にわたる認定サイクル、そして異種ダイ間のIP統合・検証の課題も、大規模展開の足かせとなっています。

Die-to-Die IP 市場の機会:

-

チップレットエコシステムの拡大により、自動車AIと新興市場におけるグローバルなDie-to-Die IPの機会が創出されます

チップレット・エコシステムがHPCやデータセンターにとどまらず、新たなエンドユース分野に拡大するにつれ、大きなビジネスチャンスが生まれています。ADASや自動運転プラットフォームを含む車載エレクトロニクスは、コンピューティング要件の高まりと安全性を重視する性能ニーズにより、高い成長ポテンシャルを秘めています。アジア太平洋地域の新興市場は、半導体製造、先進パッケージング、そして国内におけるチップ設計への積極的な投資を通じて、ビジネスチャンスを創出しています。さらに、ハイパースケーラーやシステムOEMによるカスタムシリコン開発への参入増加は、スケーラブルで標準化されたダイツーダイIPソリューションへの新たな需要を生み出しています。3Dスタッキング、ヘテロジニアスインテグレーション、そしてオープンインターフェース規格における継続的なイノベーションは、世界的な長期的な成長機会をさらに拡大するでしょう。

Xpeng の P7+ 電気セダンは、2 つの Nvidia Orin X プロセッサを使用して、複数のセンサー入力から 500 TOPS を超えるコンピューティングを実現し、モジュラー チップレットのメリットを享受できる車両での高性能コンピューティングの実際の展開を示しています。

Die-to-Die IP市場セグメント分析

-

インターフェース規格別では、UCIe(Universal Chiplet Interconnect Express)が2025年には53.43%で優位を占め、2026年から2033年にかけて9.92%という最も高いCAGRで成長すると予想されています。

-

パッケージング技術別では、2025年には2.5D ICパッケージングが39.97%で優位を占め、2026年から2033年にかけて3D ICパッケージングが10.10%という最も高いCAGRで成長すると予想されています。

-

アプリケーション別では、高性能コンピューティング (HPC) および AI アクセラレータが 2025E で 41.86% を占め、2026 年から 2033 年にかけて 9.83% という最も高い CAGR で成長すると予想されています。

-

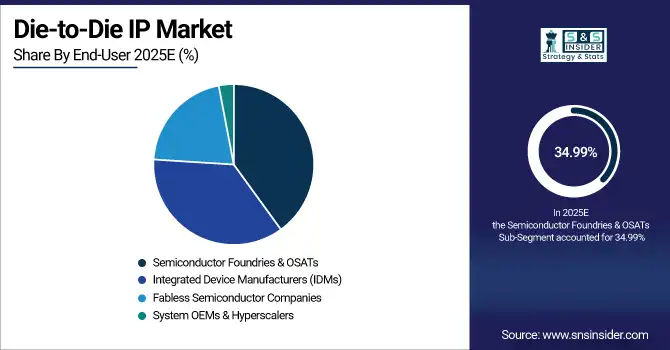

エンドユーザー別では、半導体ファウンドリおよびOSATが2025年には34.99%を占め、ファブレス半導体企業は2026年から2033年にかけて10.12%という最も高いCAGRで成長すると予想されています。

エンドユーザー別では、半導体ファウンドリが2025年以降のDie-to-Die IP市場をリードし、ファブレス企業が将来の成長を牽引

2025年以降、半導体ファウンドリとOSATは、高度なパッケージング、マルチダイ統合、そしてHPC、AI、自動車アプリケーションなど、複数のクライアントにスケーラブルなソリューションを提供する役割を担い、Die-to-Die IP市場を牽引するでしょう。ファブレス半導体企業は、標準化されたチップレットアーキテクチャとDie-to-Die IPの採用を拡大し、市場投入までの期間短縮、性能向上、設計の複雑さ軽減を目指しています。これは、ファウンドリ、システムOEM、ハイパースケーラーとの世界的な連携拡大に支えられており、2026年から2033年にかけて最も急速に成長すると予想されています。

インターフェース規格別では、UCIe規格が2025年市場を席巻し、ダイツーダイチップレット統合の急速な成長を促進

UCIe(Universal Chiplet Interconnect Express)規格は、オープンで相互運用性の高いアーキテクチャにより、異なるベンダーのチップレット間のシームレスな通信を可能にするため、2025年には主流となるでしょう。高性能コンピューティング、AIアクセラレータ、データセンタープロセッサなどへの採用が進み、業界における幅広い支持を獲得しています。UCIeは、モジュール式、高帯域幅、高エネルギー効率のマルチダイシステムへの需要増加、チップレットエコシステムの拡大、そして異種統合と高度なパッケージング技術における継続的なイノベーションを背景に、2026年から2033年にかけて最も急速に成長すると予想されています。

パッケージング技術別では、2.5D ICパッケージが2025年市場をリードし、3D ICパッケージが将来のダイツーダイの成長を加速

2.5D ICパッケージングは、その成熟度、コスト効率、そしてインターポーザー上に複数のダイを統合する能力により、2025年には主流となり、HPC、AI、データセンターアプリケーションに高性能で信頼性の高い接続を提供します。3D ICパッケージングは、AIアクセラレータ、車載エレクトロニクス、次世代コンピューティングシステムにおける相互接続密度の向上、電力効率の向上、そして高度な異種統合への需要の高まりにより、2026年から2033年にかけて最も急速に成長すると予想されています。垂直スタッキングと熱管理における継続的なイノベーションがこの成長を支えています。

アプリケーション別では、HPCとAIアクセラレータが2025年以降の急速な成長を牽引するDie-to-Die IP市場を牽引

AIワークロード、ディープラーニング、そして超高帯域幅と低レイテンシのインターコネクトを必要とする複雑なシミュレーションの急増により、2025年には高性能コンピューティング(HPC)およびAIアクセラレータがDie-to-Die IP市場を席巻するでしょう。このアプリケーションセグメントは、AIの導入拡大、エクサスケールコンピューティングへの取り組み、そしてデータセンターやクラウドプロバイダーからの需要増加に牽引され、2026年から2033年にかけて最も急速に成長すると予想されています。チップレットアーキテクチャとDie-to-Die統合における継続的なイノベーションは、HPCおよびAIシステムへの導入をさらに加速させます。

北米のDie-to-Die IP市場インサイト

北米は、2025年時点でDie-to-Die IP市場の36.36%を占めており、強力な半導体エコシステム、大手チップレットおよびIPベンダーの存在、そして先進的なパッケージングとUCIe規格の早期導入により、市場をリードする地域となっています。この地域は、多額の研究開発投資、堅牢なデータセンターインフラ、そしてAIおよびHPCアプリケーションの拡大といった恩恵を受けています。ファブレス企業、ファウンドリ、ハイパースケーラー間の緊密な連携により、北米はDie-to-Dieインターコネクト技術と高性能コンピューティングソリューションにおけるリーダーシップをさらに強化しています。

ビジネス要件に応じてカスタマイズされたレポートを入手 -今すぐお問い合わせください

米国. Die-to-Die IP 市場インサイト

米国は、大手半導体企業の集中、高度な研究開発施設、チップレット アーキテクチャの早期導入、ハイパースケーラーと高性能コンピューティング インフラストラクチャの強力な存在により、北米の Die-to-Die IP 市場を支配しています。

欧州のDie-to-Die IP市場インサイト

2025年時点でDie-to-Die IP市場の16.97%を占めるヨーロッパは、ドイツ、フランス、オランダにおける半導体イノベーションの牽引を受け、中程度のシェアを維持しています。この地域は、車載エレクトロニクス、産業オートメーション、防衛分野に注力しており、高度なパッケージング研究とチップレットに関する共同イニシアチブに支えられています。標準化、省エネルギー設計、そして政府支援による半導体プログラムへの注力は、世界のDie-to-Dieインターコネクト・エコシステムにおけるヨーロッパの役割を強化しています。

ドイツのDie-to-Die IP市場インサイト

ドイツは、強力な自動車用半導体産業、チップレットおよびパッケージング技術の高度な研究、産業オートメーションのリーダーシップにより、欧州のダイツーダイ IP 市場を支配しており、欧州のダイツーダイ相互接続エコシステムへの主要な貢献者となっています。

アジア太平洋地域のDie-to-Die IP市場インサイト

アジア太平洋地域は、中国、台湾、韓国、日本における半導体製造の急速な拡大に牽引され、2026年から2033年にかけて、Die-to-Die IP市場において10.25%という最も高いCAGRを記録すると予想されています。先進的なパッケージング、チップレット設計、そして国内の半導体イニシアチブへの投資が、この市場の普及を後押ししています。AI、HPC、コンシューマーエレクトロニクス、自動車向けアプリケーションへの需要の高まりに加え、政府の支援、そしてファブレス企業やファウンドリの存在感の高まりにより、アジア太平洋地域は世界で最も急速に成長する地域市場となっています。

中国ダイツーダイIP市場の洞察

中国は、半導体製造、高度なパッケージング施設、チップレットの研究開発、政府支援の取り組みへの巨額の投資、AI、HPC、自動車、民生用電子機器部門からの需要の増加により、アジア太平洋の Die-to-Die IP 市場を支配しています。

ラテンアメリカ(LATAM)および中東・アフリカ(MEA)のDie-to-Die IP市場インサイト

ラテンアメリカ(LATAM)と中東・アフリカ(MEA)は、Die-to-Die IP市場におけるシェアは小さいものの、成長の可能性を秘めています。LATAMは車載エレクトロニクス、産業オートメーション、新興データセンターインフラの採用拡大の恩恵を受けており、MEAは防衛、エネルギー、通信アプリケーションに重点を置いています。半導体教育への投資、現地製造への取り組み、そして世界的な技術プロバイダーとの提携により、これらの地域は徐々に能力を強化しています。北米、欧州、アジア太平洋地域に比べると採用は遅れていますが、これらの地域はニッチなアプリケーションや戦略的な拡大の機会を提供しています。

Die-to-Die IP 市場の競争環境:

シノプシス社は、ダイ間インターコネクトソリューションを含む電子設計自動化(EDA)ツールと半導体IPを提供する世界有数のプロバイダーです。高性能UCIe準拠IP、高度なPHY、コントローラ、検証プラットフォームを提供し、HPC、AI、データセンター、自動車、民生用電子機器向けのマルチダイ・チップレット・アーキテクチャを実現します。シノプシスは、ヘテロジニアス・インテグレーションと高度なパッケージングにおけるイノベーションを推進し、半導体企業の設計サイクルの加速、性能の最適化、そして信頼性の高い高帯域幅インターコネクトの実現を支援しています。

-

2024年9月、シノプシスは、マルチダイAIデータセンターチップの超高帯域幅ダイ間接続を実現する、コントローラ、PHY、検証IPを含む、ピンあたり40GbpsのUCIe IPスイートを発表しました。このソリューションは、強化されたシグナルインテグリティモニタリングと幅広いインターコネクトサポートを提供します。

Cadence Design Systems, Inc.は、電子設計自動化(EDA)ツールと半導体IPのリーディングプロバイダーであり、Die-to-Dieインターコネクトおよびチップレットソリューションを専門としています。UCIe準拠のIP、高速PHY、コントローラ、そしてHPC、AI、データセンター、自動車、コネクティビティアプリケーション向けのマルチダイアーキテクチャをサポートする検証プラットフォームを提供しています。Cadenceは、市場投入までの期間短縮、高性能な統合、そしてスケーラブルなヘテロジニアス設計を実現し、先進的なパッケージングと次世代半導体技術の世界的な普及を促進しています。

-

2025年4月、ケイデンスは、AI、HPC、モビリティ設計を加速するためにIntelの18Aおよび18A-Pテクノロジーに最適化されたUCIe 1.1 48Gダイツーダイ相互接続IPや高度なインターフェースIPなど、設計IPポートフォリオの大幅な強化を発表しました。

Die-to-Die IP 企業は次のとおりです。

-

Synopsys

-

Cadence Design Systems

-

Arm Holdings

-

Marvell Technology

-

Alphawave Semi

-

Rambus

-

Arteris

-

Blue Cheetah Analog Design

-

VeriSilicon

-

OpenFive

-

OPENEDGES Technology

-

Siemens EDA

-

Texas Instruments

-

NXP Semiconductors

-

Infineon Technologies

-

STMicroelectronics

-

Renesas Electronics

-

Microchip Technology

-

Analog Devices

-

ON Semiconductor

| レポート属性 | 詳細 |

|---|---|

| 2025年の市場規模 | 18億ドル |

| 2033年までの市場規模 | 37億2000万米ドル |

| 年平均成長率 | 2026年から2033年までのCAGRは9.57% |

| 基準年 | 2025E |

| 予測期間 | 2026~2033年 |

| 履歴データ | 2021-2024 |

| レポートの範囲と対象範囲 | 市場規模、セグメント分析、競合状況、地域分析、DROCおよびSWOT分析、予測展望 |

| 主要セグメント | • インターフェース規格別(UCIe(Universal Chiplet Interconnect Express)、BoW(Bunch of Wires)、独自仕様/カスタムインターフェース、新興オープンスタンダード) • パッケージング技術別(2.5D ICパッケージング、3D ICパッケージング、ファンアウト・ウェーハレベル・パッケージング(FOWLP)、システムインパッケージ(SiP)) • アプリケーション別(高性能コンピューティング(HPC)およびAIアクセラレータ、データセンターおよびクラウドインフラストラクチャ、コンシューマエレクトロニクス、車載エレクトロニクス) • エンドユーザー別(半導体ファウンドリおよびOSAT、統合デバイスメーカー(IDM)、ファブレス半導体企業、システムOEMおよびハイパースケーラー) |

| 地域分析/カバレッジ | 北米 (米国、カナダ)、欧州 (ドイツ、英国、フランス、イタリア、スペイン、ロシア、ポーランド、その他の欧州諸国)、アジア太平洋 (中国、インド、日本、韓国、オーストラリア、ASEAN 諸国、その他のアジア太平洋諸国)、中東およびアフリカ (UAE、サウジアラビア、カタール、南アフリカ、その他の中東およびアフリカ諸国)、ラテンアメリカ (ブラジル、アルゼンチン、メキシコ、コロンビア、その他のラテンアメリカ諸国)。 |

| 企業プロフィール | Synopsys, Cadence Design Systems, Arm Holdings, Marvell Technology, Alphawave Semi, Rambus, Arteris, Blue Cheetah Analog Design, VeriSilicon, OpenFive, OPENEDGES Technology, Siemens EDA, Texas Instruments, NXP Semiconductors, Infineon Technologies, STMicroelectronics, Renesas Electronics, Microchip Technology, Analog Devices, ON Semiconductor. |

よくある質問

回答: Die-to-Die IP 市場は、2026 年から 2033 年にかけて 9.57% の CAGR で成長すると予想されています。

回答: Die-to-Die IP 市場規模は 2025 年時点で 18 億米ドルであり、2033 年までに 37.2 億米ドルに達すると予想されています。

回答: Die-to-Die IP 市場は、チップレット アーキテクチャの採用の増加、高性能コンピューティングと AI の需要の増加、UCIe などの標準化された相互接続による 2.5D/3D パッケージングの進歩によって推進されています。

回答: UCIe (Universal Chiplet Interconnect Express) が Die-to-Die IP 市場を独占していました。

回答: 2025 年時点で、Die-to-Die IP 市場は北米が独占していました。