Mercado de propiedad intelectual de chip a chip: Alcance y descripción general del informe:

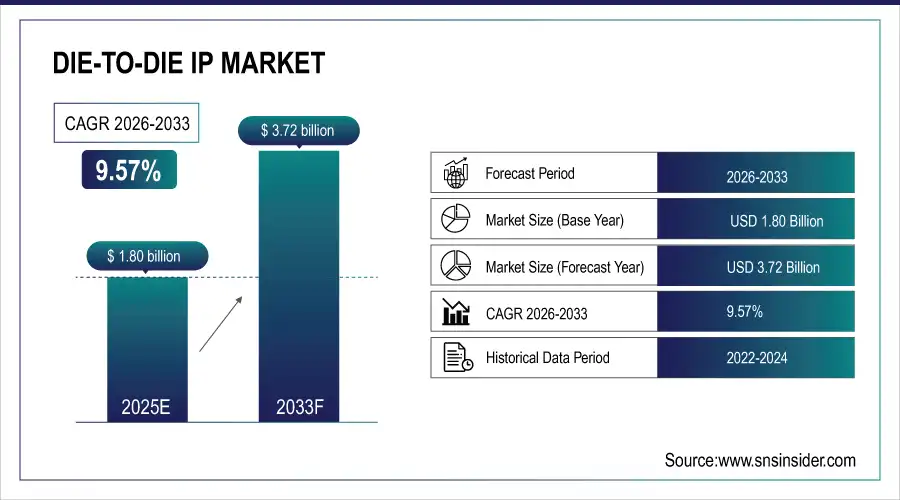

El tamaño del mercado de propiedad intelectual de matriz a matriz se valoró en USD 1.80 mil millones en 2025E y se proyecta que alcance los USD 3.72 mil millones para 2033, creciendo a una CAGR del 9,57 % durante 2026-2033.

El mercado de IP de matriz a matriz está en crecimiento debido a la rápida adopción de arquitecturas basadas en chiplets que permiten un mayor rendimiento, un menor consumo de energía y menores costos de diseño en comparación con los chips monolíticos. La creciente demanda de aceleradores de IA, computación de alto rendimiento y procesadores para centros de datos impulsa la necesidad de interconexiones de alto ancho de banda y baja latencia. Los avances en el empaquetado 2.5D y 3D, la creciente adopción del estándar UCIe y la creciente complejidad de los semiconductores impulsan aún más la expansión del mercado en aplicaciones automotrices, de consumo e industriales.

Proyección del tamaño del mercado y crecimiento:

-

Tamaño del mercado en 2025E: USD 1.800 millones

-

Tamaño del mercado en 2033: 3.720 millones de dólares

-

CAGR del 9,57% de 2026 a 2033

-

Año base 2025E

-

Período de pronóstico 2026-2033

-

Datos históricos 2021-2024

Para obtener más información sobre el mercado de propiedad intelectual de Die-to-Die, solicite un informe de muestra gratuito.

Tendencias clave del mercado de propiedad intelectual de matriz a matriz

-

Adopción rápida de arquitecturas basadas en chiplets que reemplazan los diseños SoC monolíticos tradicionales para lograr un mayor rendimiento y eficiencia.

-

Creciente demanda de procesadores de HPC, IA, aprendizaje automático y centros de datos que requieren interconexiones de matriz a matriz de baja latencia y gran ancho de banda.

-

Avances en el empaquetado de circuitos integrados (CI) 2.5D y 3D y uso creciente de estándares abiertos como UCIe para la interoperabilidad.

-

Expansión del ecosistema de chiplets a aplicaciones automotrices, ADAS y de conducción autónoma con necesidades de rendimiento críticas para la seguridad.

-

Aumento de las inversiones en la fabricación de semiconductores, empaquetado avanzado y desarrollo de silicio personalizado en Asia Pacífico por parte de hiperescaladores y OEM de sistemas.

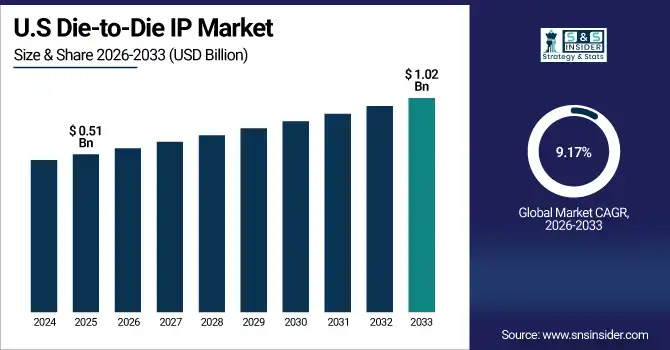

El tamaño del mercado estadounidense de IP de matriz a matriz se valoró en USD 510 millones en 2025E y se proyecta que alcance los USD 1020 millones para 2033, con una tasa de crecimiento anual compuesta (TCAC) del 9,17 % entre 2026 y 2033. Este mercado está creciendo gracias a las fuertes inversiones en IA y computación de alto rendimiento, la rápida adopción de arquitecturas de chiplets por parte de las principales empresas de semiconductores, el liderazgo en empaquetado avanzado y la creciente demanda de soluciones de interconexión de alto ancho de banda y eficiencia energética por parte de los hiperescaladores.

Factores impulsores del crecimiento del mercado de propiedad intelectual en todos sus aspectos:

-

El rápido cambio hacia arquitecturas de chiplets impulsa el crecimiento del mercado global de propiedad intelectual de matriz a matriz en la IA de HPC y el empaquetado avanzado.

El mercado global de IP de matriz a matriz se ve impulsado principalmente por la rápida transición de diseños monolíticos de sistema en chip a arquitecturas basadas en chiplets, que permiten un mayor rendimiento, una mayor productividad y menores costos de desarrollo. La creciente demanda de computación de alto rendimiento, inteligencia artificial, aprendizaje automático y procesadores para centros de datos requiere soluciones de interconexión entre múltiples matrices con un ancho de banda ultraalto, baja latencia y eficiencia energética. Los avances en tecnologías de encapsulado avanzadas, como la integración de circuitos integrados 2.5D y 3D, junto con la creciente adopción de estándares abiertos como UCIe, están acelerando la interoperabilidad y la madurez del ecosistema. Además, la creciente complejidad del diseño de semiconductores en nodos avanzados y la necesidad de optimizar la eficiencia energética y térmica están impulsando la adopción de IP de interconexión de matriz a matriz en aplicaciones de automoción, redes y electrónica de consumo.

Los diseños basados en chiplets generan actualmente alrededor de 40 mil millones de dólares en ingresos anuales, lo que demuestra cuán extendida se ha vuelto la integración modular de múltiples matrices en la electrónica de alto rendimiento.

Restricciones del mercado de propiedad intelectual de principio a fin:

-

El mercado de IP de matriz a matriz se ve limitado por los desafíos de estandarización, los diseños complejos y las limitaciones de la gestión térmica

El mercado de IP de matriz a matriz se enfrenta a limitaciones derivadas de una estandarización limitada más allá de la adopción temprana de UCIe, lo que genera desafíos de interoperabilidad entre proveedores y ecosistemas. La complejidad del diseño, los problemas de integridad de la señal a altas velocidades de datos y las limitaciones de gestión térmica en el encapsulado avanzado dificultan una adopción más rápida. Además, los largos ciclos de calificación en aplicaciones automotrices e industriales, junto con los desafíos de integración y validación de IP en matrices heterogéneas, ralentizan la implementación a gran escala.

Oportunidades de mercado de propiedad intelectual en tiempo real:

-

La expansión del ecosistema de chiplets abre oportunidades globales de propiedad intelectual de matriz a matriz en la IA automotriz y los mercados emergentes.

Existen importantes oportunidades a medida que el ecosistema de chiplets se expande a nuevos sectores de uso final, más allá de la HPC y los centros de datos. La electrónica automotriz, incluyendo los sistemas avanzados de asistencia al conductor (ADAS) y las plataformas de conducción autónoma, presenta un fuerte potencial de crecimiento debido al aumento de los requisitos de computación y las necesidades de rendimiento críticas para la seguridad. Los mercados emergentes de Asia Pacífico están generando oportunidades mediante fuertes inversiones en la fabricación de semiconductores, el empaquetado avanzado y las iniciativas nacionales de diseño de chips. Además, la creciente participación de hiperescaladores y fabricantes de equipos originales (OEM) de sistemas en el desarrollo de silicio a medida está generando una nueva demanda de soluciones IP escalables y estandarizadas de matriz a matriz. La innovación continua en apilamiento 3D, integración heterogénea y estándares de interfaz abiertos generará aún más oportunidades de crecimiento a largo plazo a nivel mundial.

El sedán eléctrico P7+ de Xpeng utiliza dos procesadores Nvidia Orin X para ofrecer más de 500 TOPS de computación a partir de múltiples entradas de sensores, lo que demuestra una implementación real de computación de alto rendimiento en vehículos que podrían beneficiarse de chiplets modulares.

Análisis del segmento de mercado de propiedad intelectual de principio a fin

-

Según el estándar de interfaz, UCIe (Universal Chiplet Interconnect Express) dominó con un 53,43 % en 2025E, y se espera que crezca a la CAGR más rápida del 9,92 % entre 2026 y 2033.

-

Según Packaging Technology, el embalaje IC 2.5D dominó con un 39,97 % en 2025E, y se espera que el embalaje IC 3D crezca a la CAGR más rápida del 10,10 % entre 2026 y 2033.

-

Por aplicación, la computación de alto rendimiento (HPC) y los aceleradores de IA dominaron con un 41,86 % en 2025E, y se espera que crezcan a la CAGR más rápida del 9,83 % entre 2026 y 2033.

-

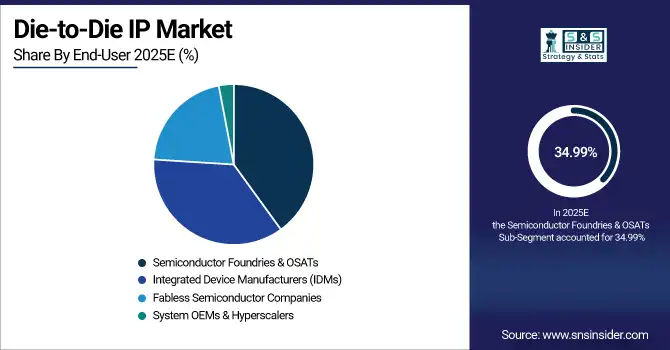

Por usuario final, las fundiciones de semiconductores y los OSAT dominaron con un 34,99 % en 2025E. Se espera que las empresas de semiconductores sin fábrica crezcan a la CAGR más rápida del 10,12 % entre 2026 y 2033.

Por usuario final, las fundiciones de semiconductores lideran el mercado de propiedad intelectual de matriz a matriz en 2025E, mientras que las empresas sin fábrica impulsan el crecimiento futuro.

Las fundiciones de semiconductores y las OSAT dominarán el mercado de propiedad intelectual de matriz a matriz en 2025E, impulsadas por su papel en el empaquetado avanzado, la integración multimatriz y la provisión de soluciones escalables para múltiples clientes en aplicaciones de HPC, IA y automoción. Se prevé que las empresas de semiconductores sin fábrica experimenten un mayor crecimiento entre 2026 y 2033, a medida que adopten cada vez más arquitecturas de chiplets estandarizadas e propiedad intelectual de matriz a matriz para acelerar el tiempo de comercialización, mejorar el rendimiento y reducir la complejidad del diseño, gracias a la creciente colaboración con fundiciones, fabricantes de equipos originales (OEM) de sistemas e hiperescaladores a nivel mundial.

Según Interface Standard, el estándar UCIe domina el mercado 2025E e impulsa un rápido crecimiento futuro en la integración de chiplets de matriz a matriz.

El estándar UCIe (Universal Chiplet Interconnect Express) es dominante en 2025E gracias a su arquitectura abierta e interoperable, que permite una comunicación fluida entre chiplets de diferentes proveedores. Su adopción en informática de alto rendimiento, aceleradores de IA y procesadores para centros de datos impulsa un amplio apoyo en la industria. Se prevé que UCIe experimente su mayor crecimiento entre 2026 y 2033, impulsado por la creciente demanda de sistemas multichip modulares, de alto ancho de banda y energéticamente eficientes, la expansión de los ecosistemas de chiplets y la continua innovación en integración heterogénea y tecnologías avanzadas de empaquetado.

Por Packaging Technology, el empaquetado de circuitos integrados 2.5D lidera el mercado de 2025E, mientras que el empaquetado de circuitos integrados 3D acelera el crecimiento futuro de matriz a matriz.

El empaquetado de circuitos integrados 2.5D dominará el mercado en 2025E gracias a su madurez, rentabilidad y capacidad para integrar múltiples matrices en un intercalador, ofreciendo alto rendimiento y conectividad fiable para aplicaciones de HPC, IA y centros de datos. Se prevé que el empaquetado de circuitos integrados 3D experimente su mayor crecimiento entre 2026 y 2033, impulsado por la creciente demanda de mayor densidad de interconexión, mayor eficiencia energética e integración heterogénea avanzada en aceleradores de IA, electrónica automotriz y sistemas informáticos de última generación. La innovación continua en apilamiento vertical y gestión térmica respalda este crecimiento.

Por aplicación, los aceleradores de HPC e IA impulsan el mercado de propiedad intelectual de matriz a matriz de 2025 con un rápido crecimiento futuro.

Los aceleradores de computación de alto rendimiento (HPC) e IA dominarán el mercado de IP de matriz a matriz en 2025E debido al aumento de las cargas de trabajo de IA, el aprendizaje profundo y las simulaciones complejas que requieren interconexiones de alto ancho de banda y baja latencia. Se prevé que este segmento de aplicaciones experimente su mayor crecimiento entre 2026 y 2033, impulsado por la creciente adopción de IA, las iniciativas de computación a exaescala y la creciente demanda de los centros de datos y los proveedores de la nube. La innovación continua en arquitecturas de chiplets y la integración de matriz a matriz acelera aún más la implementación en sistemas de HPC e IA.

Perspectivas del mercado de propiedad intelectual en América del Norte

Norteamérica, con el 36,36 % del mercado de IP de matriz a matriz en 2025E, es la región dominante gracias a su sólido ecosistema de semiconductores, la presencia de proveedores líderes de chiplets e IP, y la adopción temprana de estándares de empaquetado avanzado y UCIe. La región se beneficia de importantes inversiones en I+D, una sólida infraestructura de centros de datos y el crecimiento de las aplicaciones de IA y HPC. La estrecha colaboración entre empresas sin fábrica, fundiciones e hiperescaladores refuerza aún más el liderazgo de Norteamérica en tecnología de interconexión de matriz a matriz y soluciones de computación de alto rendimiento.

Obtenga un informe personalizado según los requisitos de su negocio: consulte ahora

EE . UU . Perspectivas del mercado de propiedad intelectual en detalle

Estados Unidos domina el mercado de propiedad intelectual de matriz a matriz de América del Norte debido a su concentración de empresas líderes de semiconductores, instalaciones avanzadas de investigación y desarrollo, adopción temprana de arquitecturas de chiplets y una fuerte presencia de hiperescaladores e infraestructura informática de alto rendimiento.

Perspectivas del mercado europeo de propiedad intelectual en detalle

Europa, que representa el 16,97 % del mercado de IP de matriz a matriz en 2025E, mantiene una participación moderada, impulsada por la innovación en semiconductores en Alemania, Francia y los Países Bajos. La región se centra en la electrónica automotriz, la automatización industrial y las aplicaciones de defensa, con el apoyo de la investigación avanzada en empaquetado y las iniciativas colaborativas de chiplets. El fuerte énfasis en la estandarización, los diseños energéticamente eficientes y los programas de semiconductores respaldados por los gobiernos refuerza el papel de Europa en el ecosistema global de interconexión de matriz a matriz.

Perspectivas del mercado de propiedad intelectual en Alemania , paso a paso

Alemania domina el mercado europeo de propiedad intelectual de matriz a matriz debido a su sólida industria de semiconductores automotrices, su investigación avanzada en tecnologías de chiplets y empaquetado y su liderazgo en automatización industrial, lo que la convierte en el principal contribuyente al ecosistema de interconexión de matriz a matriz de Europa.

Perspectivas del mercado de propiedad intelectual en Asia Pacífico

Se espera que Asia Pacífico registre la tasa de crecimiento anual compuesta (TCAC) más rápida, del 10,25 %, entre 2026 y 2033, en el mercado de propiedad intelectual de matriz a matriz, impulsada por la rápida expansión de la fabricación de semiconductores en China, Taiwán, Corea del Sur y Japón. Las inversiones en encapsulado avanzado, diseño de chiplets e iniciativas nacionales de semiconductores impulsan su adopción. La creciente demanda de IA, HPC, electrónica de consumo y aplicaciones automotrices, combinada con el apoyo gubernamental y la creciente presencia de empresas sin fábrica y fundiciones, posiciona a Asia Pacífico como el mercado regional de mayor crecimiento a nivel mundial.

Perspectivas del mercado de propiedad intelectual de China , punto por punto

China domina el mercado de propiedad intelectual de matriz a matriz de Asia Pacífico debido a sus enormes inversiones en fabricación de semiconductores, instalaciones de empaquetado avanzadas, I+D de chiplets, iniciativas respaldadas por el gobierno y la creciente demanda de los sectores de IA, HPC, automotriz y electrónica de consumo.

Perspectivas detalladas del mercado de propiedad intelectual en América Latina (LATAM) y Oriente Medio y África (MEA)

Latinoamérica (LATAM) y Oriente Medio y África (MEA) poseen una participación menor en el mercado de IP de matriz a matriz, pero muestran un potencial creciente. LATAM se beneficia de la creciente adopción de la electrónica automotriz, la automatización industrial y la infraestructura emergente de centros de datos, mientras que MEA se centra en aplicaciones de defensa, energía y telecomunicaciones. Las inversiones en formación en semiconductores, las iniciativas de fabricación local y las alianzas con proveedores de tecnología globales están fortaleciendo gradualmente las capacidades. Si bien la adopción es más lenta que en Norteamérica, Europa y Asia Pacífico, estas regiones ofrecen oportunidades para aplicaciones de nicho y expansión estratégica.

Panorama competitivo del mercado de propiedad intelectual de matriz a matriz:

Synopsys, Inc. es un proveedor líder mundial de herramientas de automatización de diseño electrónico (EDA) y propiedad intelectual (PI) de semiconductores, incluyendo soluciones de interconexión de matriz a matriz. La compañía ofrece IP de alto rendimiento compatible con UCIe, PHY avanzados, controladores y plataformas de verificación que habilitan arquitecturas de chiplet multimatriz para HPC, IA, centros de datos, automoción y electrónica de consumo. Synopsys impulsa la innovación en integración heterogénea y encapsulado avanzado, ayudando a las empresas de semiconductores a acelerar los ciclos de diseño, optimizar el rendimiento y lograr interconexiones fiables de alto ancho de banda.

-

En septiembre de 2024, Synopsys anunció una suite de IP UCIe de 40 Gbps por pin, que incluye controlador, PHY e IP de verificación para permitir una conectividad de matriz a matriz con un ancho de banda ultraalto para chips multimatriz de IA para centros de datos. La solución ofrece una monitorización mejorada de la integridad de la señal y una amplia compatibilidad con interconexiones.

Cadence Design Systems, Inc. es un proveedor líder de herramientas de automatización de diseño electrónico (EDA) y propiedad intelectual (PI) de semiconductores, especializado en soluciones de interconexión de matriz a matriz y chiplet. La empresa ofrece IP compatible con UCIe, PHY de alta velocidad, controladores y plataformas de verificación compatibles con arquitecturas multimatriz para aplicaciones de HPC, IA, centros de datos, automoción y conectividad. Cadence facilita una comercialización más rápida, una integración de alto rendimiento y diseños heterogéneos escalables, impulsando la adopción global de tecnologías avanzadas de encapsulado y semiconductores de última generación.

-

En abril de 2025, Cadence anunció una mejora significativa de su cartera de propiedad intelectual de diseño, que incluye una propiedad intelectual de interconexión de matriz a matriz UCIe 1.1 48G y una propiedad intelectual de interfaz avanzada optimizada para las tecnologías 18A y 18A-P de Intel para acelerar los diseños de IA, HPC y movilidad.

Las empresas de propiedad intelectual de Die-to-Die son:

-

Sinopsis

-

Sistemas de diseño de cadencia

-

Arm Holdings

-

Tecnología Marvell

-

Alphawave Semi

-

Rambus

-

Arteris

-

Diseño analógico de guepardo azul

-

VeriSilicon

-

OpenFive

-

Tecnología OPENEDGES

-

Siemens EDA

-

Texas Instruments

-

Semiconductores NXP

-

Tecnologías Infineon

-

STMicroelectrónica

-

Electrónica Renesas

-

Tecnología de microchip

-

Dispositivos analógicos

-

ON Semiconductor

| Atributos del informe | Detalles |

|---|---|

| Tamaño del mercado en 2025E | USD 1.80 mil millones |

| Tamaño del mercado en 2033 | USD 3.72 mil millones |

| Tasa de crecimiento anual compuesta (TCAC) | CAGR del 9,57% de 2026 a 2033 |

| Año base | 2025E |

| Período de pronóstico | 2026-2033 |

| Datos históricos | 2021-2024 |

| Alcance y cobertura del informe | Tamaño del mercado, análisis de segmentos, panorama competitivo, análisis regional, análisis DROC y FODA, pronóstico. |

| Segmentos clave | • Por estándar de interfaz (UCIe [Universal Chiplet Interconnect Express], BoW [Bunch of Wires], interfaces propietarias/personalizadas y estándares abiertos emergentes) • Por tecnología de empaquetado (empaquetado de IC 2.5D, empaquetado de IC 3D, empaquetado a nivel de oblea en abanico (FOWLP) y sistema en paquete (SiP)) • Por aplicación (computación de alto rendimiento (HPC) y aceleradores de IA, centros de datos e infraestructura en la nube, electrónica de consumo y electrónica automotriz) • Por usuario final (fundiciones de semiconductores y OSAT, fabricantes de dispositivos integrados (IDM), empresas de semiconductores fabless y OEM de sistemas e hiperescaladores) |

| Análisis/cobertura regional | América del Norte (EE. UU., Canadá), Europa (Alemania, Reino Unido, Francia, Italia, España, Rusia, Polonia, resto de Europa), Asia Pacífico (China, India, Japón, Corea del Sur, Australia, países de la ASEAN, resto de Asia Pacífico), Medio Oriente y África (EAU, Arabia Saudita, Qatar, Sudáfrica, resto de Medio Oriente y África), América Latina (Brasil, Argentina, México, Colombia, resto de América Latina). |

| Perfiles de empresas | Synopsys, Cadence Design Systems, Arm Holdings, Marvell Technology, Alphawave Semi, Rambus, Arteris, Blue Cheetah Analog Design, VeriSilicon, OpenFive, OPENEDGES Technology, Siemens EDA, Texas Instruments, NXP Semiconductors, Infineon Technologies, STMicroelectronics, Renesas Electronics, Microchip Technology, Analog Devices, ON Semiconductor. |